Alinteri J. of Agr. Sci. (2021) 36(1): 635-641 e-ISSN: 2587-2249 info@alinteridergisi.com

http://dergipark.gov.tr/alinterizbd http://www.alinteridergisi.com/ DOI:10.47059/alinteri/V36I1/AJAS21090

### **RESEARCH ARTICLE**

# Construction of pMos Logic based Low Power High Speed Comparator Compare with nMos Logic

## M. Devendra Reddy<sup>1</sup> • P. Dass<sup>2\*</sup>

<sup>1</sup>Research Scholar, Department of Electronics and Communication Engineering, Saveetha School of Engineering, Saveetha Institute of Medical and Technical Sciences, Saveetha University, Chennai, Tamil Nadu, India. E-mail: moolintidevendrareddy17@saveetha.com

<sup>2\*</sup>Project Guide, Department of Electronics and Communication Engineering, Saveetha School of Engineering, Saveetha Institute of Medical and Technical Sciences, Saveetha University, Chennai, Tamil Nadu, India. E-mail: dass@saveetha.com

#### ARTICLEINFO

Article History: Received: 10.04.2021 Accepted: 17.05.2021 Available Online: 28.06.2021

Keywords: Innovative pMos Logic based Comparator nMos Logic based Comparator Tanner Tool Power Consumption Green Energy

#### ABSTRACT

Aim: The aim of this work is to construct an innovative pMos logic based comparator and analyze the power consumption and compare with the nMos logic based comparator. Material and methods: The comparator is designed by using the Tanner tool version 16.01 for simulation and verification. By varying the length of a transistors in a circuit the power values were obtained. This experiment is performed for 20 different values of length. Results: The power consumption of a pMos logic based comparator was minimum (2.2656  $\pm$  0.37933), followed by the nMos logic based comparator (7.7494  $\pm$  0.41603), the less power consumption of power by the constructed pMos logic based comparator appears to have less power consumption than the nMos logic based comparator.

#### Please cite this paper as follows:

Devendra Reddy, M. and Dass, P. (2021). Construction of pMos Logic based Low Power High Speed Comparator Compare with nMos Logic. *Alinteri Journal of Agriculture Sciences*, 36(1): 635-641. doi: 10.47059/alinteri/V36I1/AJAS21090

#### Introduction

This method is about to design and analyse the power consumption of pMos logic based comparator and compare with nMos logic based comparator (P. Dass 2020). Today, the necessity of ultra-low power, high speed and efficient devices like ADC leads to the use of comparators to make rapid decisions (Kumar and Kumar 2016). Analog-to-Digital converters convert analogue quantities into the digital language that is used in information processing, computing, transmission, and control systems. So, digitised signals are used in almost every application. ((Varshney and Nagaria 2020). The output of high velocity analogue to digital converters is essentially determined by the comparator. Lowpower and high-speed ADCs are critical building blocks in the front-end of a radio-frequency receiver in most modern telecommunication systems (Sarfraz Hussain, Kumar, and Trivedi 2017).

Due to their important role in modern communications, speed and power consumption in mobile equipment, analogous to digital converters, were more attracted(Razavi, Tavakoli, and Setoudeh 2020).

The total number of articles published in this topic over the past five years are more than 200. A low power consumption and high speed. Gate Diffusion Input (GDI) is one technique of low energy efficiency and area efficiency. GDI's disadvantage is its low logic output swing(Swetha 2016). An XNOR port using three transistors with a power consumption analysis with eight transistors using CADENCE EDA 90nm technology (Manikannan, Mahendran, and Prabakaran 2017). A novel modified comparator is a combination of adiabatic logic 2N-2N2P and two static adiabatic clocked logic (2N-2N2P and PASCAL), efficient charge recovery logic adiabatic and two phases static adiabatic static clocked logic (ECRL and 2PASCL)(T. S. A. Samuel et al. 2017). The offset is suppressed by dynamically storing the comparator offset on the input capacitors(Liu et al. 2017). Adiabatic logic is used to produce a 1-bit adder for low power consumption (Saladi and Leela

<sup>\*</sup> Corresponding author: dass@saveetha.com

Kumari 2021). A pair of hybrid 1-bit complete adder cells that use both pass transistor and transmission gate logic and are low-power and high speed (Tirumalasetty and Machupalli 2019). The best overall work is low power consumption and high speed. Gate Diffusion Input (GDI) is one technique of low energy efficiency and area efficiency. GDI's disadvantage is its low logic output swing(Swetha 2016).

Previously our team has a rich experience in working on various research projects across multiple disciplines (Sathish and Karthick 2020; Varghese, Ramesh, and Veeraiyan 2019; S. R. Samuel, Acharya, and Rao 2020; Venu, Raju, and Subramani 2019; M. S. Samuel et al. 2019; Venu, Subramani, and Raju 2019; Mehta et al. 2019; Sharma et al. 2019; Malli Sureshbabu et al. 2019; Krishnaswamy et al. 2020; Muthukrishnan et al. 2020; Gheena and Ezhilarasan 2019; Vignesh et al. 2019; Ke et al. 2019; Vijayakumar Jain et al. 2019; Jose, Ajitha, and Subbaiyan 2020). Now the growing trend in this area motivated us to pursue this project.

The power consumption was analysed in the nMos logic based comparators but not in the pMos logic based comparators. So, The power consumption was analysed in pMos logic based comparator by varying the length of a transistors. Construction of low power digital comparator in pseudo nmos logic to reduce the power dissipation(P. Dass 2020). The aim of this study is to construct a pMos logic based comparator and analyze the power consumption and compare with the nMos logic based comparator.

#### **Materials and Methods**

The proposed work is to analyse the power consumption of pmos logic based comparator. The study is done in the Department of ECE, Saveetha School of Engineering and this work is not done by using the human samples. The total no of groups used in this project is 2. Group 1 is the pmos comparator (Experimental group) and group 2 is the nmos comparator (Control group). 20 samples were taken for the analysis of power consumed by the constructed comparator with the g power of 80%(Vijay et al. 2017).

The comparator was designed using the Tanner tool for simulation and verification. pMos logic is a family of digital circuits based on p-channel, enhancement mode metal-oxidesemiconductor field effect transistor. 20 different values of length of transistor were taken for the analysis. Same values of length were taken for both the groups (S. Hussain, Kumar, and Trivedi 2021).

In the existing system, N-type metal-oxide-semiconductor logic uses n-type MOSFETs to implement logic gates and other digital circuits. These nMOS transistors operate by creating an inversion layer in a p-type transistor body. The n-channel is created by applying voltage to the third terminal, called the gate (Vijay et al. 2017). In this comparator, 20 different values of length and width and analysis of power consumption was done. The design setup is simulated as a standard protocol (Shashank Shekhar 2015).

The power consumption values of designed and existing models for different values of length of transistors in a comparator as given in table 1.

| Table 1. The power consumption values of designed and            |

|------------------------------------------------------------------|

| existing models for different values of length of transistors in |

| a comparator.                                                    |

| Length(nm) | Power           | Power consumption  |  |  |

|------------|-----------------|--------------------|--|--|

|            | consumption of  | of nMos comparator |  |  |

|            | pMos comparator | (milliwatts)       |  |  |

|            | (milliwatts)    |                    |  |  |

| 90         | 1.393           | 8.771              |  |  |

| 100        | 1.592           | 8.287              |  |  |

| 120        | 1.789           | 7.738              |  |  |

| 150        | 1.982           | 7.149              |  |  |

| 180        | 2.011           | 8.596              |  |  |

| 200        | 2.058           | 7.289              |  |  |

| 220        | 2.109           | 7.299              |  |  |

| 250        | 2.183           | 7.538              |  |  |

| 280        | 2.254           | 7.43               |  |  |

| 300        | 2.299           | 7.532              |  |  |

| 320        | 2.342           | 7.574              |  |  |

| 350        | 2.404           | 7.63               |  |  |

| 380        | 2.462           | 7.622              |  |  |

| 400        | 2.5             | 7.834              |  |  |

| 420        | 2.535           | 7.675              |  |  |

| 450        | 2.587           | 7.685              |  |  |

| 480        | 2.636           | 8.033              |  |  |

| 500        | 2.688           | 7.616              |  |  |

| 520        | 2.699           | 7.652              |  |  |

| 580        | 2.788           | 8.039              |  |  |

The SPSS version 2.1 Statistical software is used to compare the power values of pMos logic based comparator with the nMos logic based comparator. Descriptive statistics (mean, standard deviation, and standard error) were carried out for each model. This will give the mean, standard deviation, and standard error of the comparators. The independent variables in this study are Voltage source, length, width. The dependent variable is power. The analysis done on this work was the power consumption of a pMos logic based comparator compared with nMos logic comparator.

#### Results

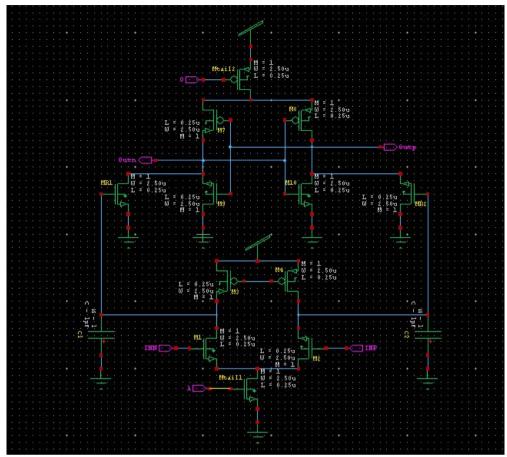

Fig.1: it shows that the pMos logic based Comparator design in the S-Edit in tanner tool and simulation is done. Here, the 5 pMos transistors and 6 nMos transistors are used. When input is low the pMos transistors will work and simulate the comparator. Fig.2 it showed the power consumption of a pMos logic based comparator which is designed in a tanner tool at 90nm length of a transistors in a comparator. The power consumption in the designed comparator is low when compared with the existing models.

Fig.1. Represents the schematic diagram of a Pmos logic-based comparator

Fig.2. Represents the graph shows the power consumption of a pMos logic based comparator

In performing statistical analysis of 20 samples, pMos comparator obtained 0.38 standard deviation with 0.08 standard error while nMos comparator obtained 0.42 standard

deviation with 0.09 standard error (Table 2). The standard deviation in Pmos comparator is low.

Table 2. shows the Mean, standard deviation, standard errors of the power consumption of a pMos logic comparator and nmos logic comparator independent sample t test was performed

| Group | Mean   | Ν  | Std.Deviation | Std.Error Mean |  |

|-------|--------|----|---------------|----------------|--|

| pMos  | 2.2656 | 20 | 0.37933       | 0.08482        |  |

| nMos  | 7.7494 | 20 | 0.41603       | 0.09303        |  |

Table.3: it shows that the mean standard deviation and significance difference of power consumption. The significant

difference was observed between the group(p=0.955) from the independent sample test.

# **Table 3.** Shows that the mean standard deviation and significance difference of power consumption. The significant difference was observed between the group(p=0.955) from the independent sample test

|                                   | Levene's Test for<br>Equality of<br>Variances |      | t-test for Equality of Means |        |                     |                    |                          |                            |                                            |

|-----------------------------------|-----------------------------------------------|------|------------------------------|--------|---------------------|--------------------|--------------------------|----------------------------|--------------------------------------------|

|                                   | F                                             | sig  | t                            | df     | Sig. (2-<br>tailed) | Mean<br>Difference | Std. Error<br>Difference | 95%<br>Confidence<br>Lower | 95% Confidence<br>Interval of the<br>Upper |

| Equal<br>variances<br>assumed     | .003                                          | .955 | -<br>43.561                  | 38     | .000                | -5.48390           | .12589                   | -5.73875                   | -5.22905                                   |

| Equal<br>variances not<br>assumed |                                               |      | -<br>43.561                  | 37.681 | .000                | -5.48390           | .12589                   | -5.73882                   | -5.22898                                   |

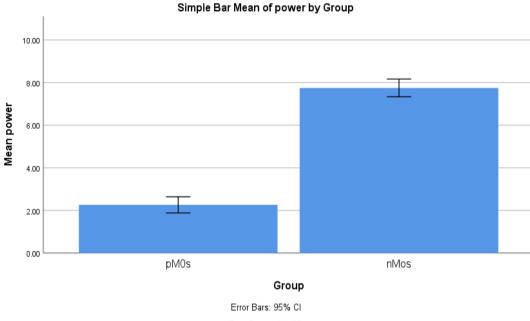

Figure.3: represents the comparison of power consumption of pMos logic based comparator and the nMos logic based comparator. It shows the power consumption of pMos logic based comparator is less and nMos logic based

comparator is more. The mean power of pMos comparator is better than the nMos comparator.

Error Bars: +/- 1 SD

**Fig.3.** Comparison of pMos logic based comparator and nMos logic based comparator in terms of power. The mean power of the pMos comparator is better than the nMos comparator. pMos comparator vs nMos comparator Y Axis: - Mean power of detection  $\pm 1$  SD.

#### Discussions

In this method, the power consumption of pMos logic based comparator appears to consume less power compared with the nMos logic based comparator. We observed that the statistically insignificant and value obtained is 0.955.

The analysis of power consumption of pMos logic based comparator by varying the length of a transistors was done. At the input of the compare preamplifier and the latch stage, pMOS transistors are used. A special, local clock generator controls both phases. The lock is activated at the evaluation stage in time to achieve sufficient preamplification and prevent excess power consumption(Khorami and Sharifkhani 2018). At the first and second phases of the comparator input, PMOS transistors are used. The second phase is enabled in a pre-amplifier gain in the evaluation phase following the first phase by a predefined delay. In addition, following the delay, the first stage is shut down to reduce overall energy consumption (Khorami, Dastjerdi, and Ahmadi 2016).

Our institution is passionate about high quality evidence based research and has excelled in various fields ((Vijayashree Priyadharsini 2019; Ezhilarasan, Apoorva, and Ashok Vardhan 2019; Ramesh et al. 2018; Mathew et al. 2020; Sridharan et al. 2019; Pc, Marimuthu, and Devadoss 2018;

#### PN

Ramadurai et al. 2019). We hope this study adds to this rich legacy.

Delay analysis of the low voltage dynamic comparator body-driven p-channel metal oxide semiconductor(Vijay et al. 2017). To achieve low electricity consumption by their mechanisms which modify circuit operation. The techniques are pseudo NMOS, CVSL, and power gating. Cascode Voltage Switch Logic. Renewable comparator at 90 nm CMOS with a supply voltage of 0.7 V is initially simulated (Khatak, Kumar, and Dhull 2018). For high speed applications with low power supply voltage, a new structure of the dynamic latch comparator is proposed. Each inverter contains a condenser which disconnects PMOS and NMOS gates(Ni et al. 2018). In our study, the tanner tool is used to simulate which is the best tool to design the comparators and calculate the power values. In this work, the power consumption as literature has reported less consumption in pMos logic comparator when compared with nMos logic comparator(P. Dass 2020). By varying the lengths of transistors in a comparator influence negatively. Here, the pMos transistor is used in design for reducing the power consumption. In the future we can use CMOS transistors to reduce power consumption.

#### Conclusion

By varying the difference length of transistors the pMos logic based comparator consumes less power. Thus, the results appear that the pMos logic-based comparator provides significantly less power consumption than the nmos logic-based comparator.

#### Declarations

#### **Conflict of Interests**

No conflict of interest in this manuscript.

#### Authors Contributions

Author MDR was involved in simulation and data analysis, manuscript writing. Author PD was involved in conceptualization, data validation, and critical review of manuscript.

#### Acknowledgement

The authors would like to express their gratitude towards Saveetha School of engineering, Saveetha Institute of Medical and Technical Sciences (Formerly known as Saveetha University) for providing the necessary infrastructure to carry out this work successfully.

#### Funding

We thank the following organizations for providing financial support that enabled us to complete the study.

- 1. Vee Eee Technologies Solution Pvt. Ltd., Chennai.

- 2. Saveetha University

- 3. Saveetha Institute of Medical and Technical Sciences.

- 4. Saveetha School of Engineering.

#### References

- Ezhilarasan, Devaraj, Velluru S. Apoorva, and Nandhigam Ashok Vardhan. 2019. "Syzygium Cumini Extract Induced Reactive Oxygen Species-Mediated Apoptosis in Human Oral Squamous Carcinoma Cells." Journal of Oral Pathology & Medicine: Official Publication of the International Association of Oral Pathologists and the American Academy of Oral Pathology 48 (2): 115-21.

- Gheena, S., and D. Ezhilarasan. 2019. "Syringic Acid Triggers Reactive Oxygen Species-Mediated Cytotoxicity in HepG2 Cells." Human & Experimental Toxicology 38 (6): 694-702.

- Hussain, Sarfraz, Rajesh Kumar, and Gaurav Trivedi. 2017. "A Novel Low Power High Speed BEC for 2GHz Sampling Rate Flash ADC in 45nm Technology." 2017 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS).

https://doi.org/10.1109/inis.2017.36.

Hussain, S., R. Kumar, and G. Trivedi. 2021. "Comparison of NMOS and PMOS Input Driving Dynamic Comparator in 45nm Technology." *IOP Conference Series: Materials Science and Engineering*.

https://doi.org/10.1088/1757-899x/1020/1/012022.

- Jose, Jerry, Ajitha, and Haripriya Subbaiyan. 2020. "Different Treatment Modalities Followed by Dental Practitioners for Ellis Class 2 Fracture - A Questionnaire-Based Survey." The Open Dentistry Journal 14 (1): 59-65.

- Ke, Yang, Mohammed Saleh Al Aboody, Wael Alturaiki, Suliman A. Alsagaby, Faiz Abdulaziz Alfaiz, Vishnu Priya Veeraraghavan, and Suresh Mickymaray. 2019. "Photosynthesized Gold Nanoparticles from Catharanthus Roseus Induces Caspase-Mediated Apoptosis in Cervical Cancer Cells (HeLa)." Artificial Cells, Nanomedicine, and Biotechnology 47 (1): 1938-46.

- Khatak, Anil, Manoj Kumar, and Sanjeev Dhull. 2018. "Analysis of CMOS Comparator in 90nm Technology with Different Power Reduction Techniques." International Journal of Electrical and Computer Engineering (IJECE). https://doi.org/10.11591/ijece.v8i6.pp4922-4931.

- Khorami, Ata, Mahmood Baraani Dastjerdi, and Ali Fotowat Ahmadi. 2016. "A Low-Power High-Speed Comparator for Analog to Digital Converters." 2016 IEEE International Symposium on Circuits and Systems (ISCAS). https://doi.org/10.1109/iscas.2016.7538971.

- Khorami, Ata, and Mohammad Sharifkhani. 2018. "A Low-Power High-Speed Comparator for Precise Applications." IEEE Transactions on Very Large Scale Integration (VLSI) Systems. https://doi.org/10.1109/tvlsi.2018.2833037.

- Krishnaswamy, Haribabu, Sivaprakash Muthukrishnan, Sathish Thanikodi, Godwin Arockiaraj Antony, and Vijayan Venkatraman. 2020. "Investigation of Air Conditioning Temperature Variation by Modifying the Structure of Passenger Car Using Computational Fluid Dynamics." Thermal Science 24 (1 Part B): 495-98.

- Kumar, Dinesh, and Manoj Kumar. 2016. "Design of Low Power Two Bit Magnitude Comparator Using Adiabatic Logic." 2016 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS). https://doi.org/10.1109/ispacs.2016.7824703.

- Liu, Jia, Fule Li, Weitao Li, Hanjun Jiang, and Zhihua Wang. 2017. "A Flash ADC with Low Offset Dynamic Comparators." 2017 International Conference on Electron Devices and Solid-State Circuits (EDSSC). https://doi.org/10.1109/edssc.2017.8126480.

- Malli Sureshbabu, Nivedhitha, Kathiravan Selvarasu, Jayanth Kumar V, Mahalakshmi Nandakumar, and Deepak Selvam. 2019. "Concentrated Growth Factors as an Ingenious Biomaterial in Regeneration of Bony Defects after Periapical Surgery: A Report of Two Cases." *Case Reports in Dentistry* 2019 (January): 7046203.

- Manikannan, G., K. Mahendran, and P. Prabakaran. 2017. "Low Power High Speed Full Adder Cell with XOR/XNOR Logic Gates in 90nm Technology." 2017 International Conference on Technical Advancements in Computers and Communications (ICTACC). https://doi.org/10.1109/ictacc.2017.25.

- Mathew, M. G., S. R. Samuel, A. J. Soni, and K. B. Roopa. 2020. "Evaluation of Adhesion of Streptococcus Mutans, Plaque Accumulation on Zirconia and Stainless Steel Crowns, and Surrounding Gingival Inflammation in Primary ...." *Clinical Oral Investigations*. https://link.springer.com/article/10.1007/s00784-020-03204-9.

- Mehta, Meenu, Deeksha, Devesh Tewari, Gaurav Gupta, Rajendra Awasthi, Harjeet Singh, Parijat Pandey, et al. 2019. "Oligonucleotide Therapy: An Emerging Focus Area for Drug Delivery in Chronic Inflammatory Respiratory Diseases." Chemico-Biological Interactions 308 (August): 206-15.

- Muthukrishnan, Sivaprakash, Haribabu Krishnaswamy, Sathish Thanikodi, Dinesh Sundaresan, and Vijayan Venkatraman. 2020. "Support Vector Machine for Modelling and Simulation of Heat Exchangers." Thermal Science 24 (1 Part B): 499-503.

- Ni, Ya-Bo, Ting Li, Zheng-Bo Huang, Yong Zhang, and Shi-Liu Xu. 2018. "A High-Speed Dynamic Comparator with Low-Power Supply Voltage." 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT). https://doi.org/10.1109/icsict.2018.8565749.

- Pc, J., T. Marimuthu, and P. Devadoss. 2018. "Prevalence and Measurement of Anterior Loop of the Mandibular Canal Using CBCT: A Cross Sectional Study." *Clinical Implant Dentistry and Related Research*. https://europepmc.org/article/med/29624863.

- P. Dass, Dr J. Mohana. 2020. "CONSTRUCTION OF LOW POWER DIGITAL COMPARATOR IN PSEUDO NMOS LOGIC TO REDUCE THE POWER DISSIPATION." Journal of Critical Reviews. https://doi.org/10.31838/jcr.07.12.367.

- Ramadurai, Neeraja, Deepa Gurunathan, A. Victor Samuel, Emg Subramanian, and Steven J. L. Rodrigues. 2019.

"Effectiveness of 2% Articaine as an Anesthetic Agent in Children: Randomized Controlled Trial." *Clinical Oral Investigations* 23 (9): 3543-50.

- Ramesh, Asha, Sheeja Varghese, Nadathur D. Jayakumar, and Sankari Malaiappan. 2018. "Comparative Estimation of Sulfiredoxin Levels between Chronic Periodontitis and Healthy Patients - A Case-Control Study." Journal of Periodontology 89 (10): 1241-48.

- Razavi, Bagher, Mohammad Bagher Tavakoli, and Farbod Setoudeh. 2020. "Approach for Low Power High Speed 4-bit Flash Analogue to Digital Converter." *IET Circuits, Devices & Systems.*

https://doi.org/10.1049/iet-cds.2018.5504.

- Saladi, Krishna, and B. Leela Kumari. 2021. "Adiabatic Logic-Based Area- and Energy-Efficient Full Adder Design." Lecture Notes in Electrical Engineering. https://doi.org/10.1007/978-981-15-8439-8\_10.

- Samuel, Melvin S., Jayanta Bhattacharya, Sankalp Raj, Needhidasan Santhanam, Hemant Singh, and N. D. Pradeep Singh. 2019. "Efficient Removal of Chromium (VI) from Aqueous Solution Using Chitosan Grafted Graphene Oxide (CS-GO) Nanocomposite." International Journal of Biological Macromolecules 121 (January): 285-92.

- Samuel, Srinivasan Raj, Shashidhar Acharya, and Jeevika Chandrasekar Rao. 2020. "School Interventions-Based Prevention of Early-Childhood Caries among 3-5-Year-Old Children from Very Low Socioeconomic Status: Two-Year Randomized Trial." Journal of Public Health Dentistry 80 (1): 51-60.

- Samuel, T. S. Arun, T. S. Arun Samuel, National Engineering College, Kovilpatti, India, S. Darwin, N. Arumugam, et al. 2017. "Design of Adiabatic Logic based Comparator for Low Power and High Speed Applications." ICTACT Journal on Microelectronics. https://doi.org/10.21917/ijme.2017.0064.

- Sathish, T., and S. Karthick. 2020. "Wear Behaviour Analysis on Aluminium Alloy 7050 with Reinforced SiC through Taguchi Approach." Journal of Japan Research Institute for Advanced Copper-Base Materials and Technologies 9 (3): 3481-87.

- Sharma, Parvarish, Meenu Mehta, Daljeet Singh Dhanjal, Simran Kaur, Gaurav Gupta, Harjeet Singh, Lakshmi Thangavelu, et al. 2019. "Emerging Trends in the Novel Drug Delivery Approaches for the Treatment of Lung Cancer." Chemico-Biological Interactions 309 (August): 108720.

- Shashank Shekhar, Dr S. R. P. Sinha. 2015. "Design and Analysis of Dynamic Comparator with Reduced Power and Delay." *International Journal of Science and Research (IJSR)* 4 (11): 1025-29.

- Sridharan, Gokul, Pratibha Ramani, Sangeeta Patankar, and Rajagopalan Vijayaraghavan. 2019. "Evaluation of Salivary Metabolomics in Oral Leukoplakia and Oral Squamous Cell Carcinoma." Journal of Oral Pathology & Medicine: Official Publication of the International Association of Oral Pathologists and the American Academy of Oral Pathology 48 (4): 299-306.

- Swetha, S. 2016. "Design of Low Power and Area Efficient Full Adder Using Modified Gate Diffusion Input." International Journal of Computer Applications. https://doi.org/10.5120/ijca2016910778.

- Tirumalasetty, Venkata Rao, and Madhusudhan Reddy Machupalli. 2019. "Design and Analysis of Low Power High-Speed 1-Bit Full Adder Cells for VLSI Applications." International Journal of Electronics. https://doi.org/10.1080/00207217.2018.1545256.

- Varghese, Sheeja Saji, Asha Ramesh, and Deepak Nallaswamy Veeraiyan. 2019. "Blended Module-Based Teaching in Biostatistics and Research Methodology: A Retrospective Study with Postgraduate Dental Students." Journal of Dental Education 83 (4): 445-50.

- Varshney, Vikrant, and Rajendra Kumar Nagaria. 2020. "Design and Analysis of Ultra High-Speed Low-Power Double Tail Dynamic Comparator Using Charge Sharing

Scheme." AEU - International Journal of Electronics and Communications. https://doi.org/10.1016/j.aeue.2020.153068.

- Venu, Harish, V. Dhana Raju, and Lingesan Subramani. 2019. "Combined Effect of Influence of Nano Additives, Combustion Chamber Geometry and Injection Timing in a DI Diesel Engine Fuelled with Ternary (diesel-Biodiesel-Ethanol) Blends." Energy 174 (May): 386-406.

- Venu, Harish, Lingesan Subramani, and V. Dhana Raju. 2019. "Emission Reduction in a DI Diesel Engine Using Exhaust Gas Recirculation (EGR) of Palm Biodiesel Blended with TiO2 Nano Additives." *Renewable Energy* 140 (September): 245-63.

- Vignesh, R., Ditto Sharmin, C. Vishnu Rekha, Sankar Annamalai, and Parisa Norouzi Baghkomeh. 2019. "Management of Complicated Crown-Root Fracture by Extra-Oral Fragment Reattachment and Intentional Reimplantation with 2 Years Review." Contemporary Clinical Dentistry 10 (2): 397-401.

- Vijayakumar Jain, S., M. R. Muthusekhar, M. F. Baig, P. Senthilnathan, S. Loganathan, P. U. Abdul Wahab, M. Madhulakshmi, and Yogaen Vohra. 2019. "Evaluation of Three-Dimensional Changes in Pharyngeal Airway Following Isolated Lefort One Osteotomy for the Correction of Vertical Maxillary Excess: A Prospective Study." Journal of Maxillofacial and Oral Surgery 18 (1): 139-46.

- Vijayashree Priyadharsini, Jayaseelan. 2019. "In Silico Validation of the Non-Antibiotic Drugs Acetaminophen and Ibuprofen as Antibacterial Agents against Red Complex Pathogens." *Journal of Periodontology* 90 (12): 1441-48.

- Vijay, Savani, N. M. Devashrayee, Assistant Professor, Department of Electronics and Communication Engineering, Institute of Technology, Nirma University, Gujarat, et al. 2017. "ANALYSIS AND DESIGN OF BODY DRIVEN DYNAMIC LATCH BASED COMPARATOR IN LOW SUPPLY VOLTAGES WITH nMOS DRIVER." *I-Manager's Journal on Electronics* Engineering. https://doi.org/10.26634/jele.7.4.13683.

641